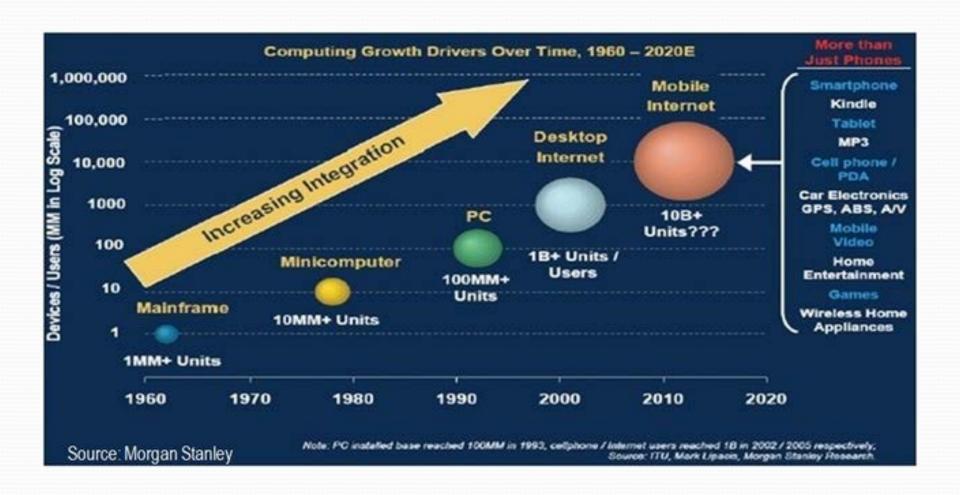

# MOSFET – A Final Outlook

**PROCESSORS** microprocessors

## Samsung teams with GlobalFoundries on 3D chips

Apr 17, 2014 3:15 PM | 🖶

Samsung is partnering with chip manufacturer GlobalFoundries to increase the supply of low-power, high-speed chips for smartphones and tablets.

GlobalFoundries has licensed Samsung's 14-nanometer FINFET chip making process, which is used to manufacture 3D transistors. Those transistors will allow GlobalFoundries to make chips that are 20 percent faster and use 35 percent less power than chips made using its current 20-nanometer technology, the companies said.

GlobalFoundries doesn't use the chips itself. It's a foundry supplier, which means it makes chips for other companies that outsource their chip production, such as Advanced Micro Devices, Nvidia and Qualcomm.

Chip makers are constantly racing to build faster, more power-efficient chips, and the deal with Samsung will help GlobalFoundries compete better with other foundry suppliers such as Taiwan's TSMC.

In fact, GlobalFoundries had been pursuing its own 14-nanometer technology, which it planned to introduce this year. It has now dropped that technology, apparently deciding that Samsung's FINFET process is a better option.

## **Electronics** Weekly.com

Multimedia Companies Home News Blogs Events Newsletters Jobs

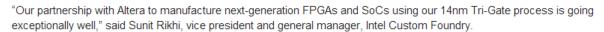

You are here: Electronics Weekly > News > General > Intel to make multi-die 14nm finfet devices with Altera

#### Intel to make multi-die 14nm finfet devices with Altera

Richard wilson 28th March 2014 Get news by email

Altera and Intel are working together on the development of multi-die devices which integrate 14nm Stratix 10 FPGAs with memory, processors and analogue components in a single package.

The heterogeneous multi-die devices incorporate 3D silicon technology and Intel's 14nm Tri-Gate (finfet) process technology.

Intel is already manufacturing Altera's Stratix 10 FPGAs and system-on-chip devices (SoCs) using the 14nm Tri-Gate process.

Intel and Altera are currently developing test vehicles aimed at streamlining manufacturing and integration flows.

"Our close collaboration enables us to work together in many areas related to semiconductor manufacturing and packaging." said Rikhi

Together, both companies are building off one another's expertise with the primary focus on building industry-disrupting products."

According to Brad Howe, senior vice president of R&D at Altera, access to Intel's manufacturing and chip packaging capabilities is allowing the FPGA supplier to offer system-in-a-package products which are "critical to meeting overall performance requirements."

#### Related news:

Altera: 14nm Stratix and 20nm Arria FPGA details

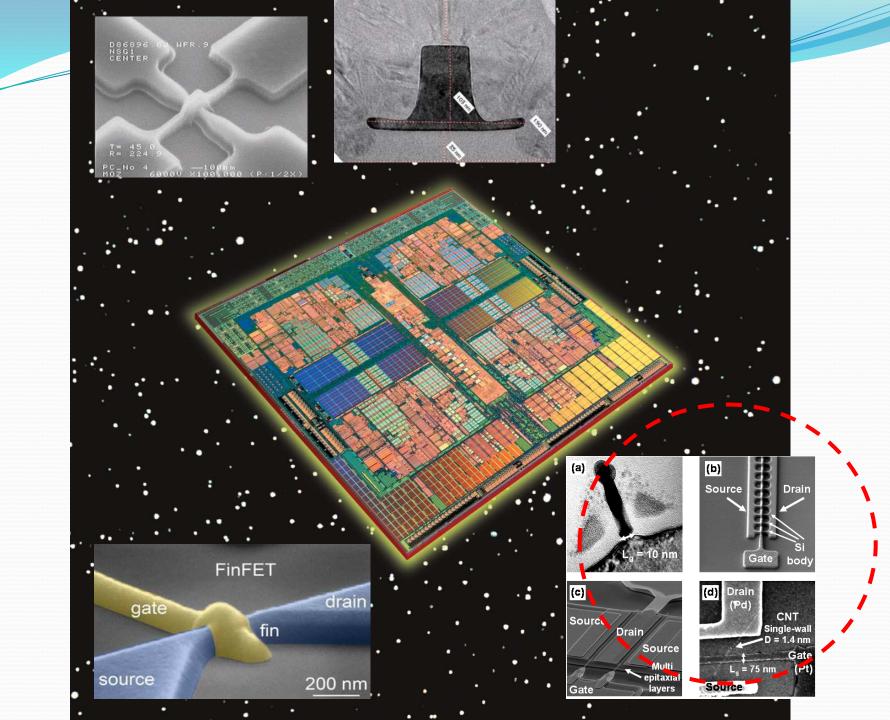

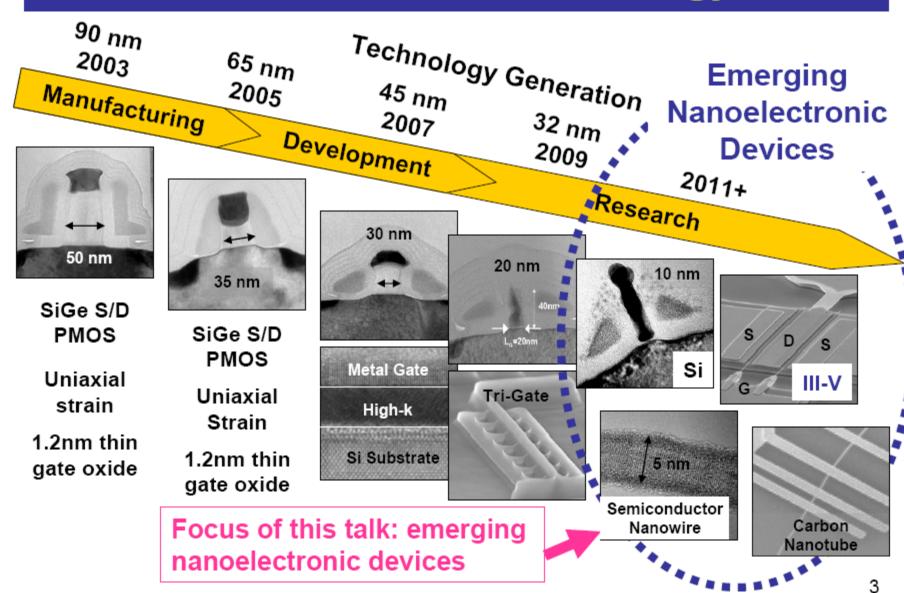

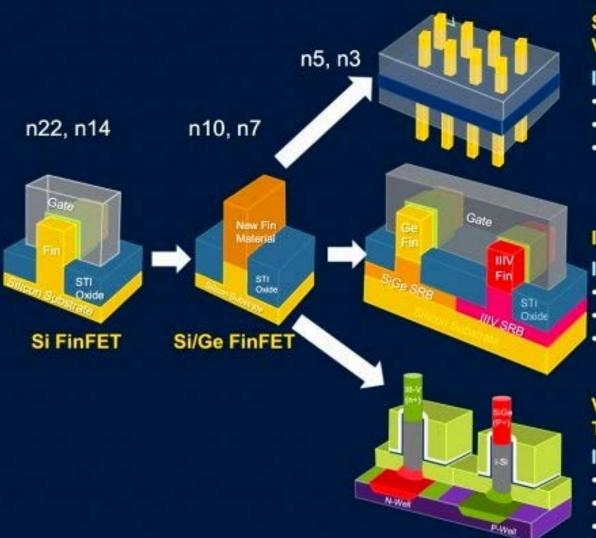

## **Transistor Nanotechnology**

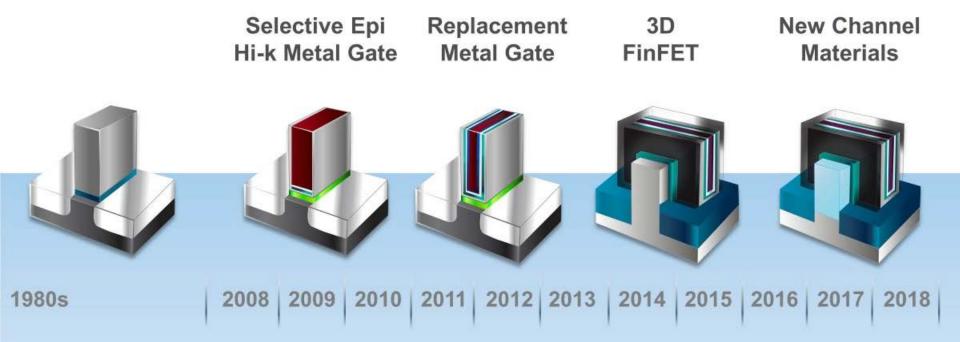

Note: Future options subject to change

## The TRANSISTOR Evolution

High Performance Low Power Transistors Enabled By Innovations in Device Architecture & Process Technologies

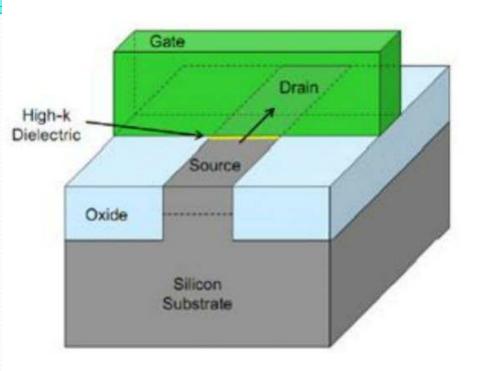

## **Traditional Planar**

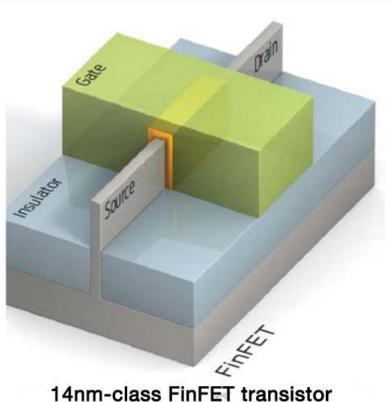

Traditional 2-D planar transistor form a conducting channel in the silicon region under the gate electrode when in the "on" state

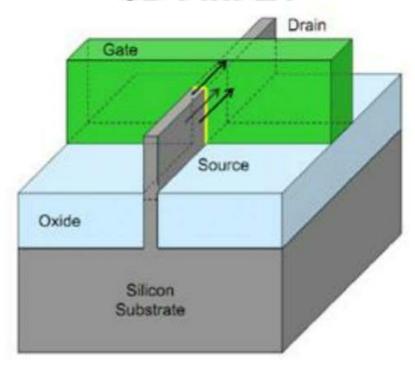

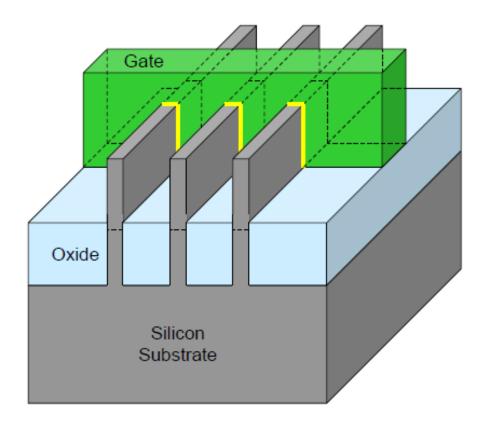

### 3D FinFET

3-D Tri-Gate transistor form conducting channels on three sides of a vertical fin structure, providing "fully depleted" operation

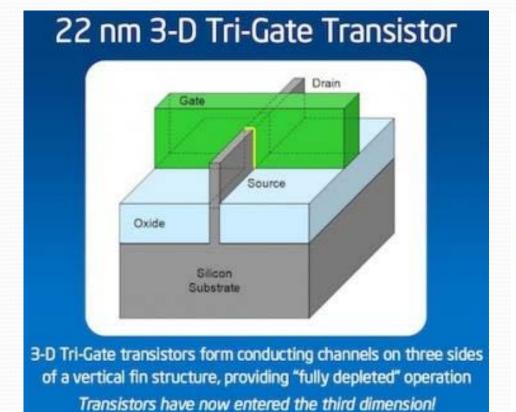

## 22 nm Tri-Gate Transistor

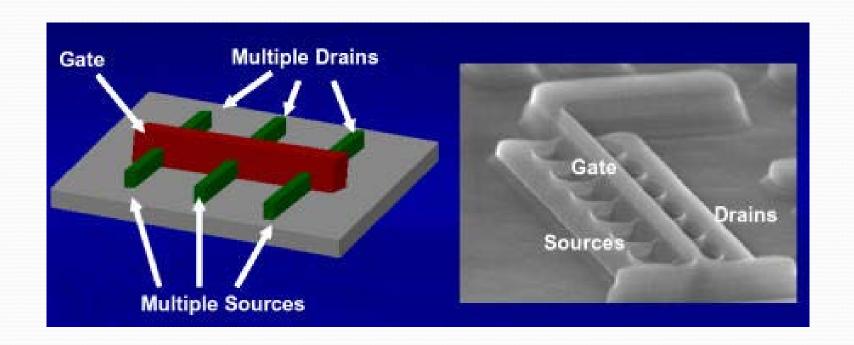

Tri-Gate transistors can have multiple fins connected together to increase total drive strength for higher performance

## **Transistor Pathway**

#### Si/Ge Gate All Around (GAA) Vertical or Horizontal

#### Improved electrostatics

- Precision etch and CMP

- Scaled metals

- High Aspect Ratio ALD

#### **III-V FinFET**

#### Improved mobility

- Epi structure

- III-V gate interface

- New material CMP

#### Vertical TFET

#### Improved SS

- Epi structure

- Multi-pass CMP

- Precision etch & CMP

External Use

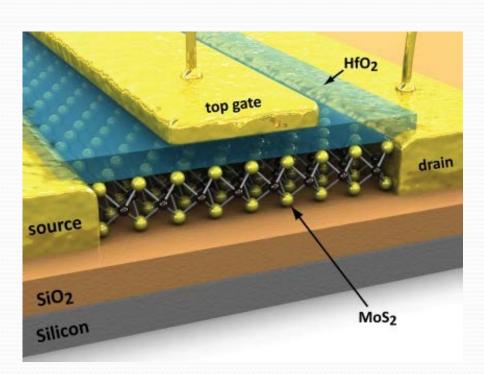

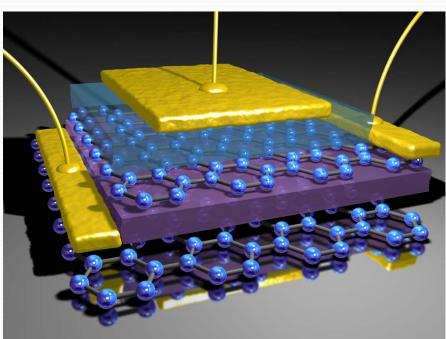

# Non-Conventional Channel Materials?

Molybdenum Disulfide

Graphene

See http://spectrum.ieee.org/nanoclast/semiconductors/materials/cause-of-2d-molybdenum-disulfides-electronic-shortcomings-revealed

## Roadmap to the future