# **Integrated Circuits**

# Introduction

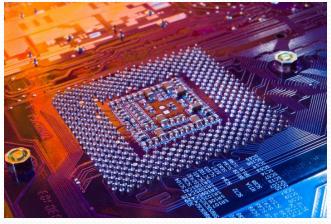

## Integrated Circuits

- Its importance is well-known

- Invention of Jack Kilby and Robert Noyce

A scientific milestone: first transistor (Bell Labs 1947) A technological milestone: Kilby's integrated circuit, TI (1959)

## Milestones

- 1959: First IC

- ... then a lot of nice ICs,...but they "can't change much" (not programmable)

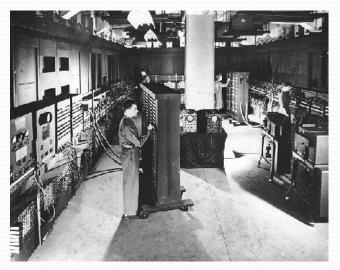

ENIAC

Source: wiki

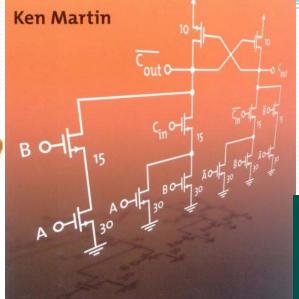

#### Digital Integrated Circuit Design

## Click to LOOK INSIDE!

#### DIGITAL INTEGRATED CIRCUITS A DESIGN PERSPECTIVE SECOND EDITION

JAN M. RABAEY ANANTHA CHANDRAKASAN BORIVOJE NIKOLIC

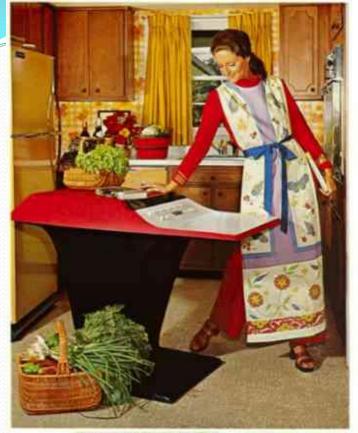

#### If she can only cook as well as Honeywell can compute.

Her smallten an supreme. Her meat planning a strailonge? Brief a what the Hohmysell people had its traid where they with a cross-reference. To her heat the support with a cross-reference. To her facultations are been ables a constraint to her facultation and the settisk. And if also patient during pushing a fee fullow competite with the week programming contention between the facility therein one 644. (0.000) to competite with the week programming contention for the settisk of the constraint factors ables a constraint data the one programming contenbles the over 1,000 retiges 500 if 700 get the Politics, 376 of non-tenned 20 disc restaurant's beet keep sector resigned 3.00 (20) Extreme 540 Her tabled aprox, non-stail, ours appres by Got (20) Coll Tringstry Resenption colling and colling appreciate or many patients provide by Gottom 28 (00 1,00) Tringstry Resen-

# Honeywell kitchen computer

| TECHNICAL INFORMATION                                                |  |  |

|----------------------------------------------------------------------|--|--|

| H316 - Kitchen computer                                              |  |  |

| Honeywell                                                            |  |  |

| Home Computer                                                        |  |  |

| J.S.A.                                                               |  |  |

| 1969                                                                 |  |  |

| Recipes were programmed into it, but language/software is<br>unknown |  |  |

| Small array of buttons and switches                                  |  |  |

| Unknown                                                              |  |  |

| 2.5 MHz                                                              |  |  |

| 4 KB magnetic core, expandable to 16 KB                              |  |  |

| Unknown                                                              |  |  |

| Unknown, probably some kind of text display                          |  |  |

| 150 pounds                                                           |  |  |

| Magnetic core memory                                                 |  |  |

| 475W at 125vAC                                                       |  |  |

| Unless you count the cutting boardunknown                            |  |  |

| \$10,600                                                             |  |  |

|                                                                      |  |  |

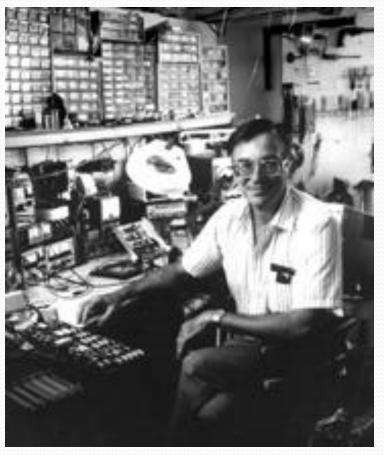

# Milestones

- 1971: Microprocessor: The story of Intel & Busicom, Ted (Marcian) Hoff

- Silicon-gated MOS

- 4004 with ~2000 transistors

http://www.pcworld.com/article/24 3954/happy\_birthday\_4004\_intels\_ first\_microprocessor\_turns\_the\_big \_40.html

# What drive technology?

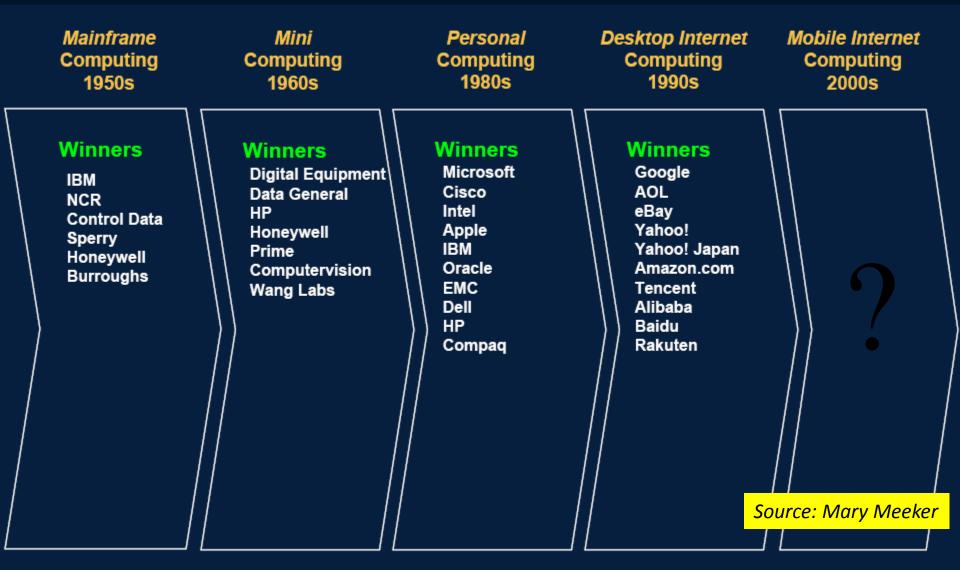

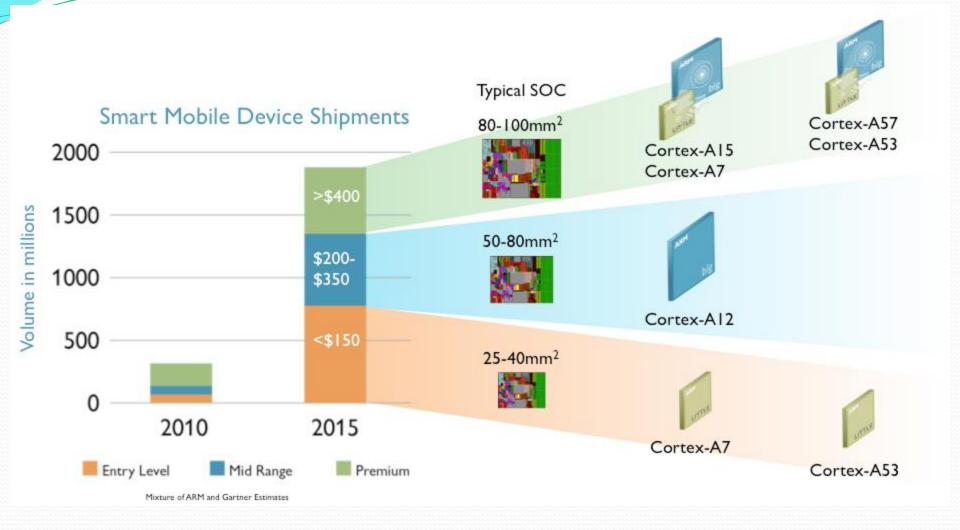

#### Mobile Internet Next Major Computing Cycle

Morgan Stanley

Source: Mary Meeker

#### Technology Cycles - Wealth Creation / Destruction New Companies Often Win Big in New Cycles

#### Morgan Stanley

Note: Winners from 1950s to 1980s based on Fortune 500 rankings (revenue-based), desktop Internet winners based on wealth created from 1995 to respective peak market capitalizations. Source: Factset, Fortune, Morgan Stanley Research.

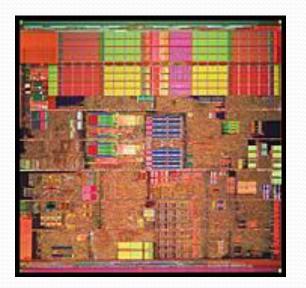

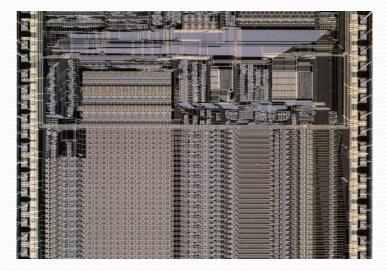

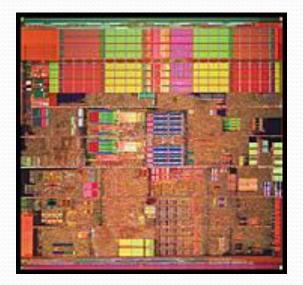

## "Smart" ICs

Field Programmable Gate Array (FPGA)

TMS320F240

#### Microprocessor

ARMA Corect Mis

# FPGA vs. Microprocessor

#### FPGA Pentium

• IC technology supports very diverse architecture

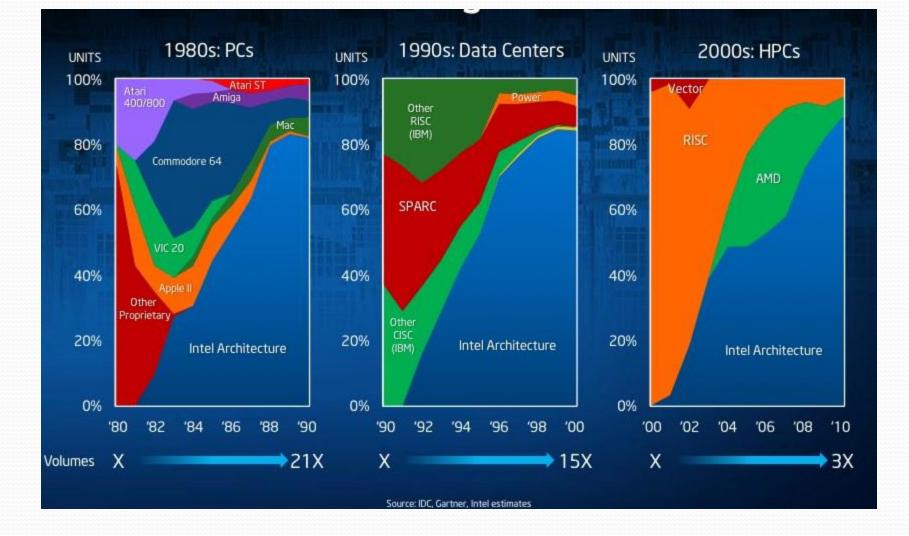

# The "Old-Time Story" of RISC vs. CISC

ARM

x86

Specialized architectures for different applications

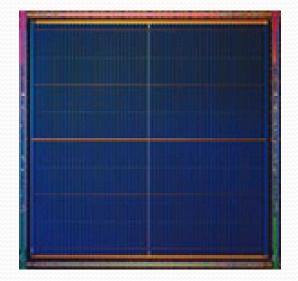

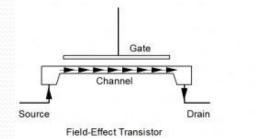

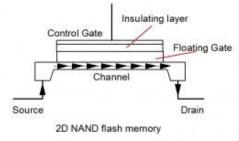

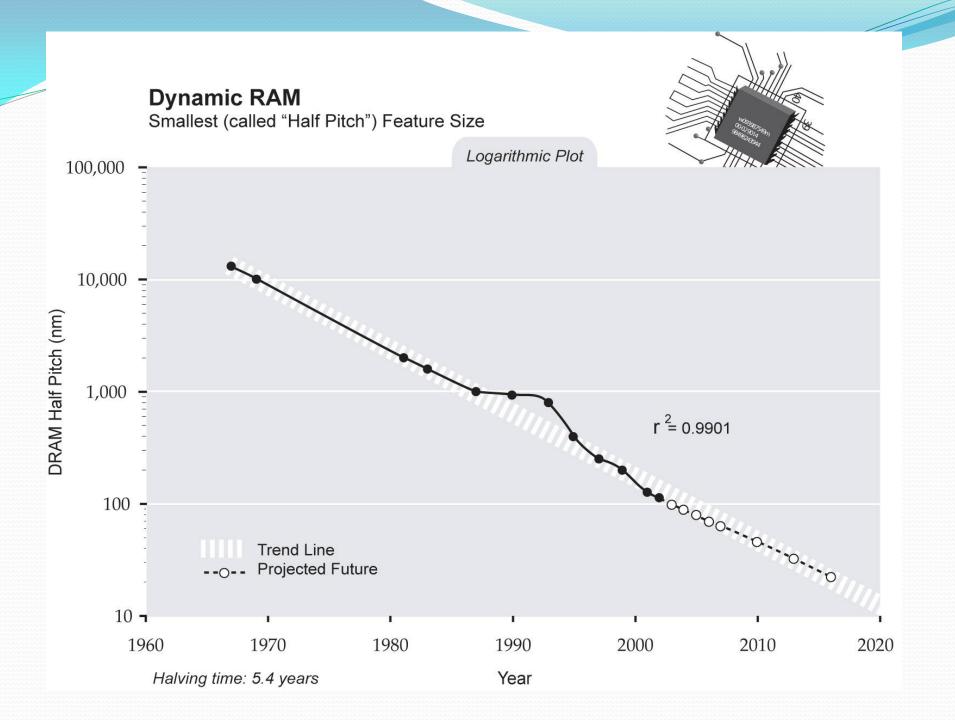

# Memory IC's

#### SRAM

#### DRAM

#### Non-volatile RAM

#### NAND flash SSD

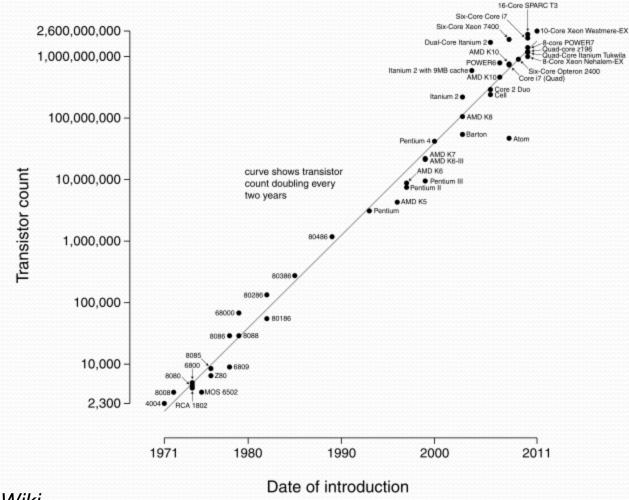

| Microprocessor                                        | Year of<br>Introduction | Transistors |

|-------------------------------------------------------|-------------------------|-------------|

| 4004                                                  | 1971                    | 2,300       |

| 8008                                                  | 1972                    | 2,500       |

| 8080                                                  | 1974                    | 4,500       |

| 8086                                                  | 1978                    | 29,000      |

| Intel286                                              | 1982                    | 134,000     |

| Intel386" processor                                   | 1985                    | 275,000     |

| Intel486 <sup>™</sup> processor                       | 1989                    | 1,200,000   |

| Intel <sup>®</sup> Pentium <sup>®</sup> processor     | 1993                    | 3,100,000   |

| Intel <sup>®</sup> Pentium <sup>®</sup> II processor  | 1997                    | 7,500,000   |

| Intel <sup>®</sup> Pentium <sup>®</sup> III processor | 1999                    | 9,500,000   |

| Intel® Pentium® 4 processor                           | 2000                    | 42,000,000  |

| Intel® Itanium® processor                             | 2001                    | 25,000,000  |

| Intel® Itanium® 2 processor                           | 2003                    | 220,000,000 |

| Intel® Itanium® 2 processor (9MB cache)               | 2004                    | 592,000,000 |

\_\_\_\_

#### Moore's law Microprocessor Transistor Counts 1971-2011 & Moore's Law

Source: Wiki

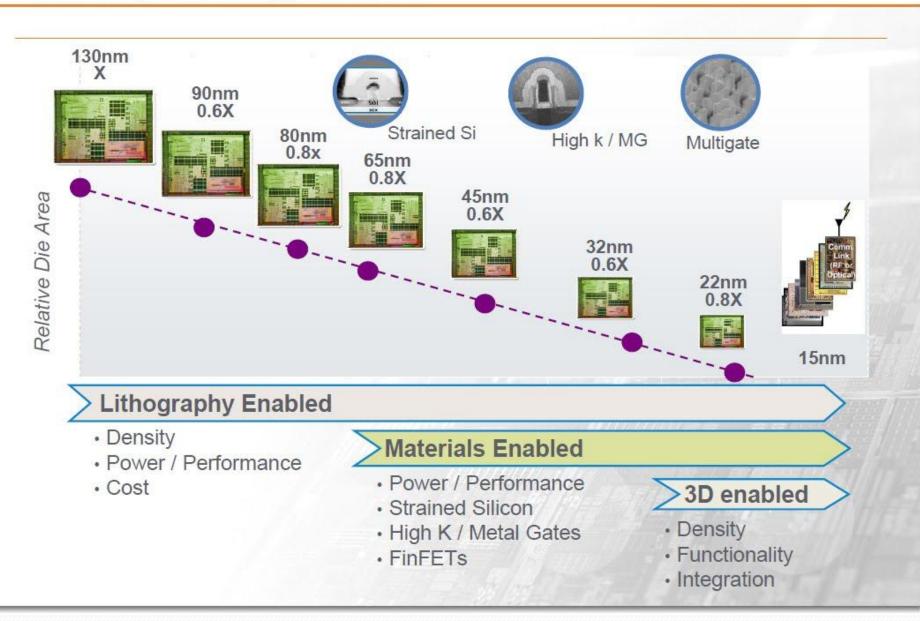

# Key Enabling Technologies For ICs

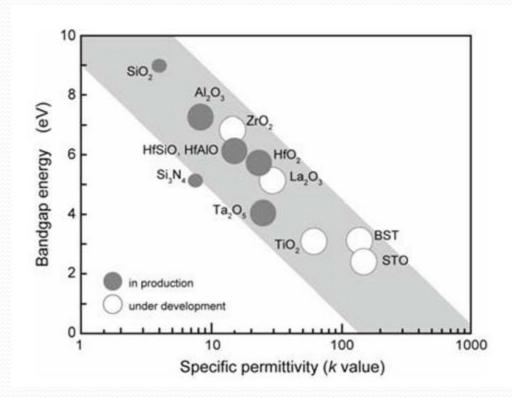

# **Crucial elements of IC technology**

- Devices and materials

- Transistor design and scaling

- Semiconductors and advanced materials

- Fabrication technology (Front end):

- feature size: how small can a transistor gate be?

- how to pack many T's in a very small area: VLSI, ULSI

- device structure: beyond planar, 2D constraint

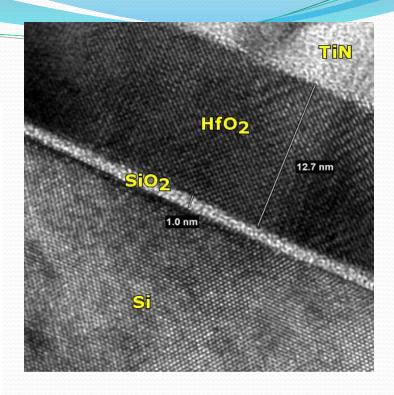

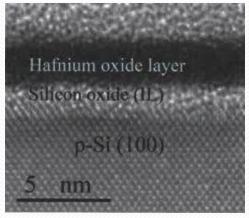

- how to make high-performance oxides, insulators

- how to make contact, "wiring"?

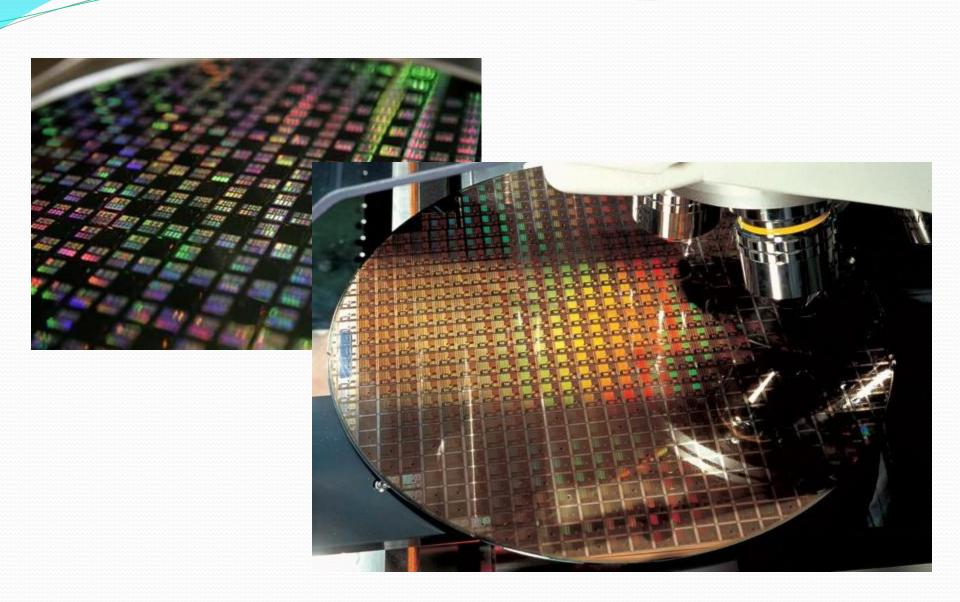

- wafer scaling

- Chip packaging technology (Back end)

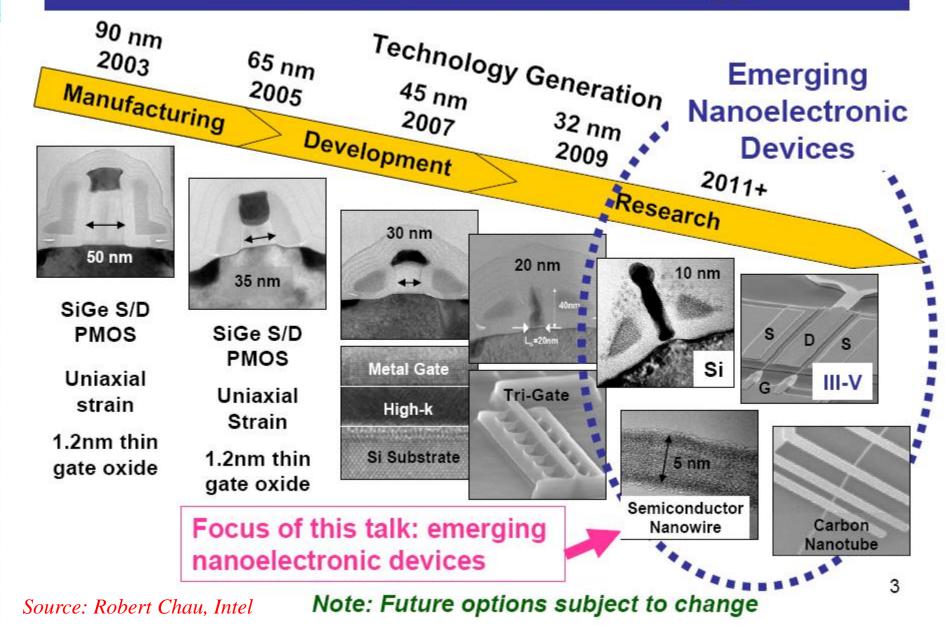

## **Transistor Nanotechnology**

## How small can the transistor be?

Past prediction

The ultimate limit of the transistor is ~ 10  $\mu$ m 1961

... On a pentium (~2002), it was ~ 0.1  $\mu m$

... And they think: 0.015  $\mu m$  is the ultimate limit

Don't bet your money on it!

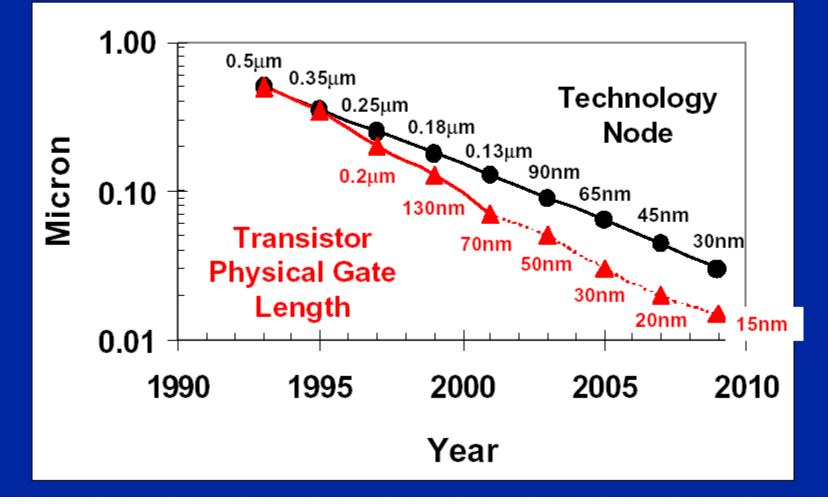

# Transistor Physical Gate Length Trend (Lithography generation > L<sub>GATE</sub>)

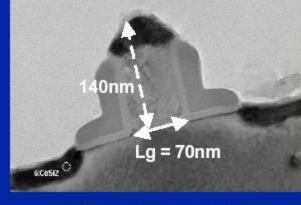

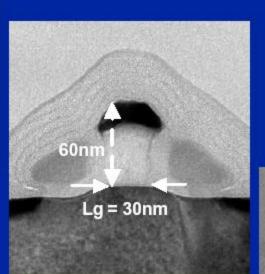

# **Transistor Scaling Continues**

70nm transistor (in production)

#### 30nm transistor (production 2005)

In 2005

20nm transistor (research phase)

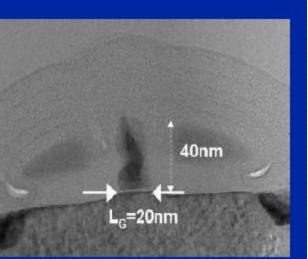

## Intel Transistor Leadership

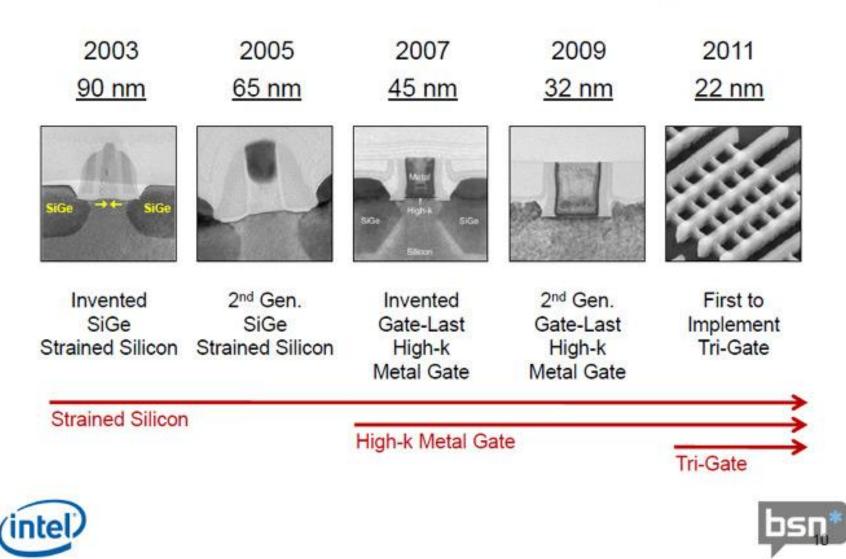

## Introducing 14XM (eXtreme Mobility)

bsn

Foundry's first innovative 14nm FinFET

Our solution is focused on:

- Rapid Time to Market (TTM)

- Ultra-Low Power

- Lowest risk path to high-volume manufacturing

In production

CON

Competitive Cost and Performance

1 year!

#### In development

GLOBALFOUNDRIES'

#### In 2010

#### Newest Manufacturing Technology Delivers Ivy Bridge

(intel)

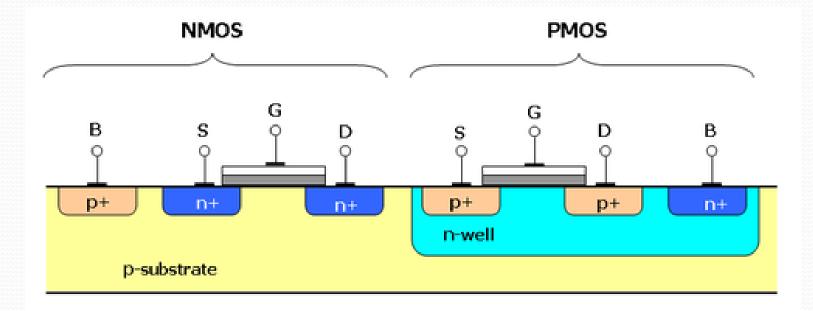

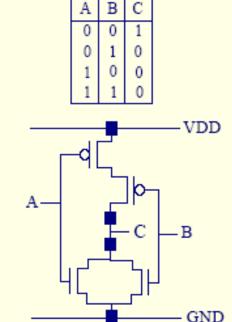

# Dual logics: CMOS

# CMOS: a key to VLSI/ULSI

#### *Remember HW on p-channel?*

# Why CMOS?

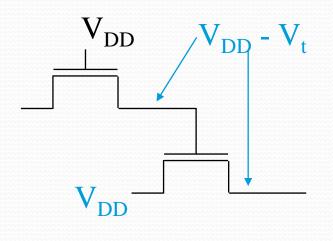

Threshold voltage requirement: voltage drop in each stage: example: n-channel

n-channel MOSFET is "natural" for logic 0 (ex. ON: +5

V) , p-channel MOSFET is "natural" for logic 1 (ex. OFF: +5 V). Together: CMOS

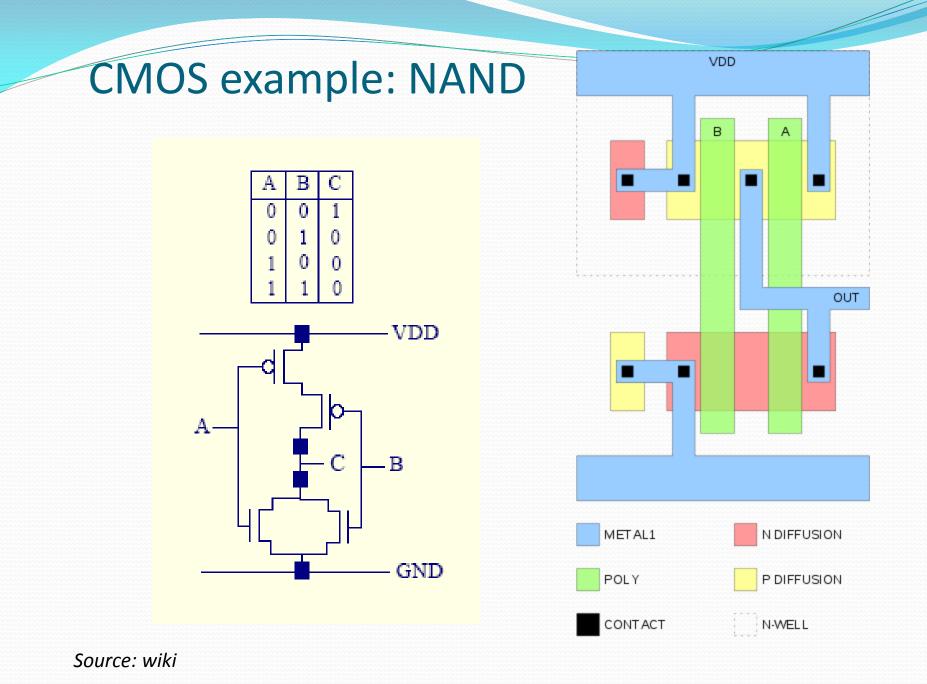

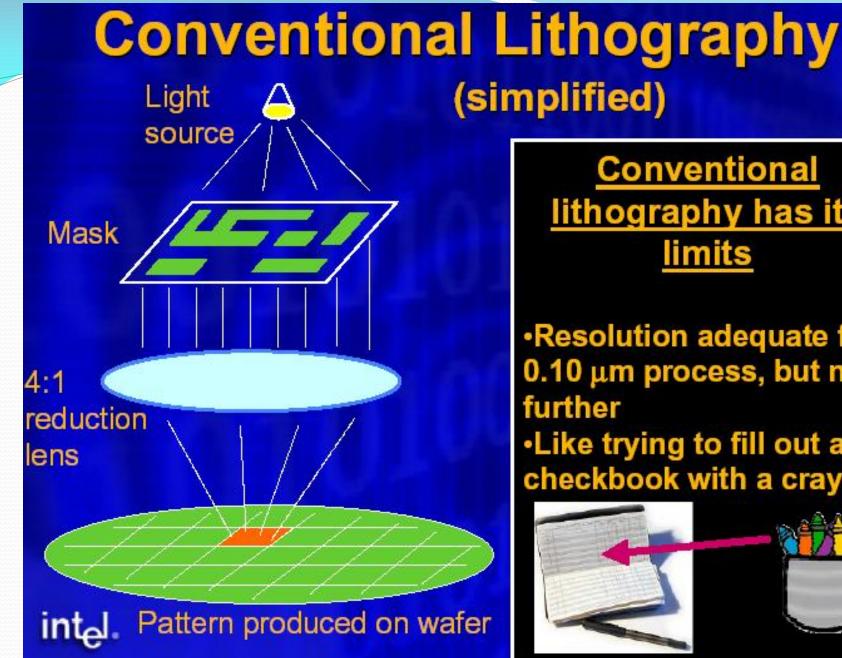

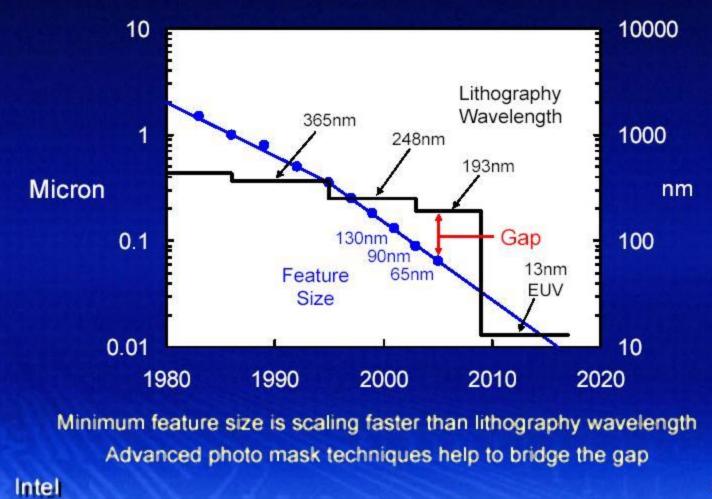

Shrinking devices require increasing resolution lithography

Conventional lithography has its

Resolution adequate for 0.10 µm process, but no Like trying to fill out a checkbook with a crayon

Figure 2 The lens for DUV photolithography with the highest NA: Starlith 1900 from Carl Zeiss. The height of the lens is more than 1 m. The optical design and ray path are schematics and given only as an illustration. The inset depicts a resist structure of 36.5-nm half-pitch, obtained with the lens at full scanning speed. Main image courtesy of Zeiss; inset courtesy of ASML.

http://www.nature.com/nphoton/journal/v1/n11/covers/tech\_f ocus\_index.html

# Lithography Challenge

# What is Extreme Ultraviolet Lithography (EUVL)?

EUV lithography uses extremely short wavelength light (factor of 20 shorter than today's lithography processes)

Visible light – 400 to 700 nm DUV lithography – 193 and 248 nm EUV lithography – 13 nm

Will be used first in 2005 by leading edge companies for critical lithography steps to produce 70 nm patterns for advanced circuit manufacturing to intellaintain Moore's Law

# **ITRS** lithography roadmap

#### Lithography friendly design rules 2007 2013 2010 2016 2019 2008 2009 2011 2012 2017 2018 2005 2006 2014 2015 2020 2021 DRAM 1/2 Pitch 45nm 65mm 32nm 22nm 16nm DRAM Hat-ptch 193nm 65 193nm immersion with water Flash Half pitch 193nm immersion with water Narrow 193nm immersion with other fluids 45 options EVU, ML2 EUV 193nm immersion with other fluids and lens material Innovative 193nm immersion with water Narrow -----32 options Imprint\_ML2 EUV Narrow 22 Innovative 193nm immersion options Imprint, ML2, innovative technology Innovative technology Narrow 16 Innovative EUV, imprint, ML2 oblions Research Required Development Underway C Qualification/Pre-Production INNINI Continuous Improvement This legend indicates the time during which research, development, and qualification/pre-production should be taking place for the solution.

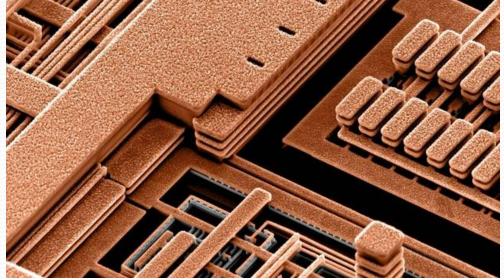

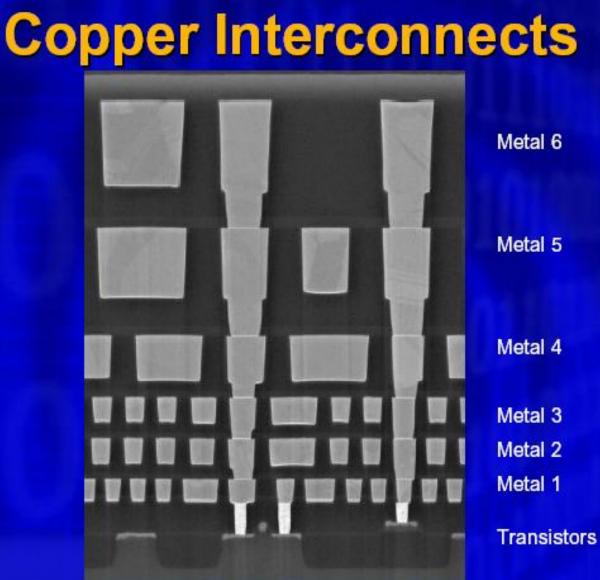

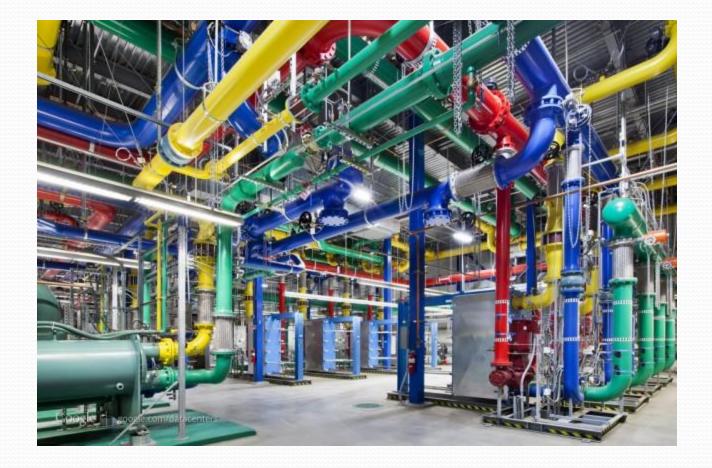

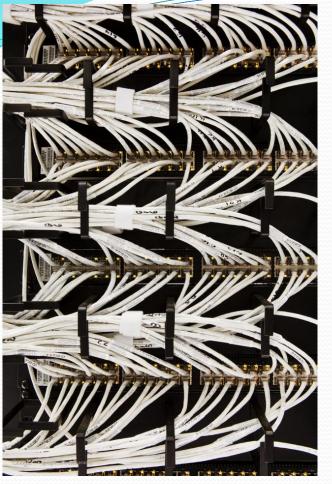

Connecting devices at high density requires good conductor

# Metal Interconnect

- For many years... It has been aluminum

- 30+ years of research for a better conductor: copper

- Copper technology has finally arrived within the last 20 years...

Source: http://www-03.ibm.com/ibm/history/ibm100/us/en/icons/copperchip/

6 Layers of Damascene Copper

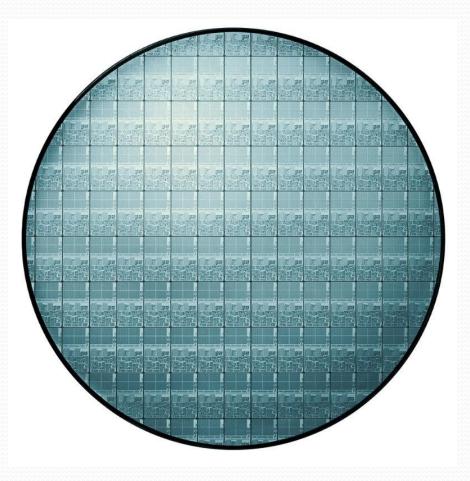

Price pressure: more devices per wafer – the advantage of economy of scale

### More chips per wafer

# The economy of scales

Large wafer...

Lots of chips (require high yield)

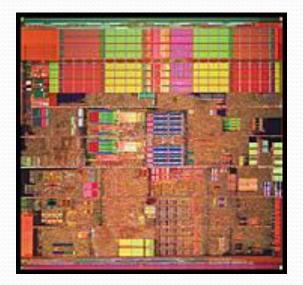

# **Chip architecture**

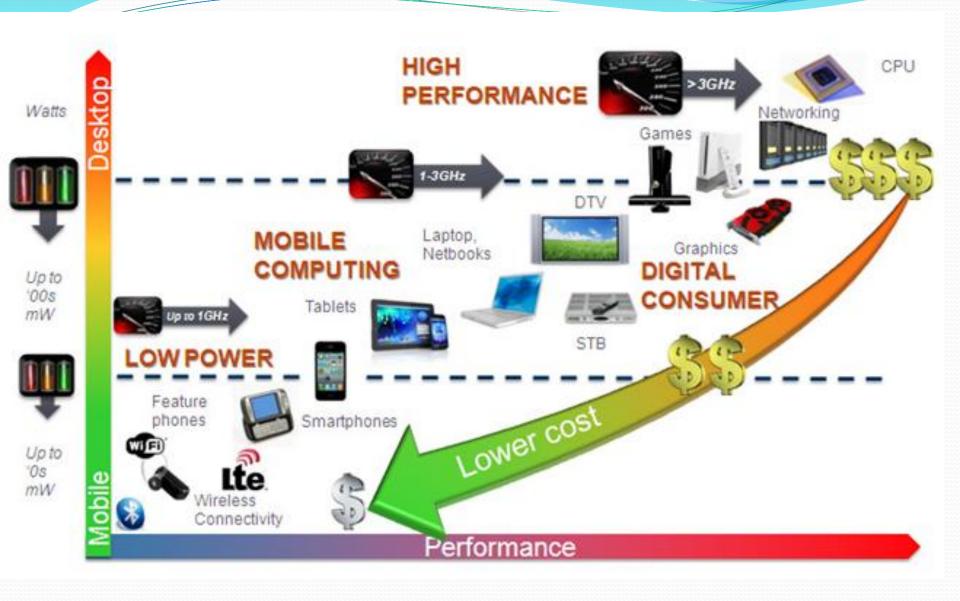

# **Application/Market-driven**

Not just size and integration, architecture is very apps-driven

# The "Old-Time Story" of RISC vs. CISC

ARM

x86

Specialized architectures for different applications

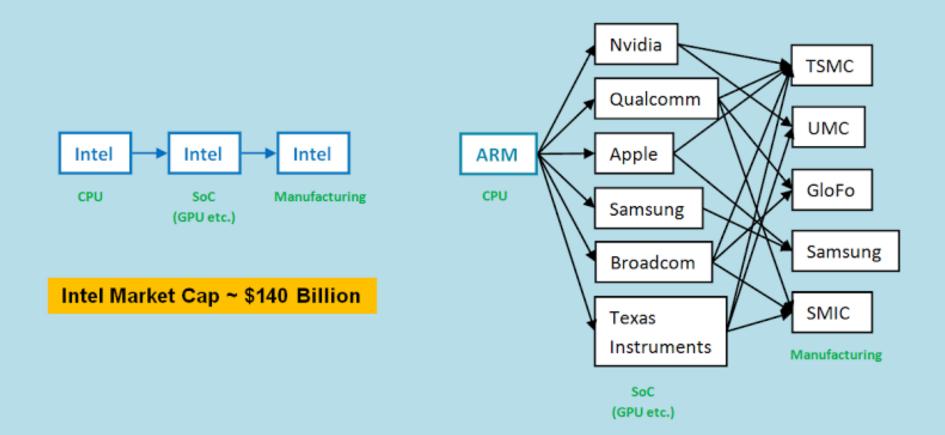

### Intel vs. ARM

kartik.jayan@gmail.com March 2012

\_\_\_\_\_

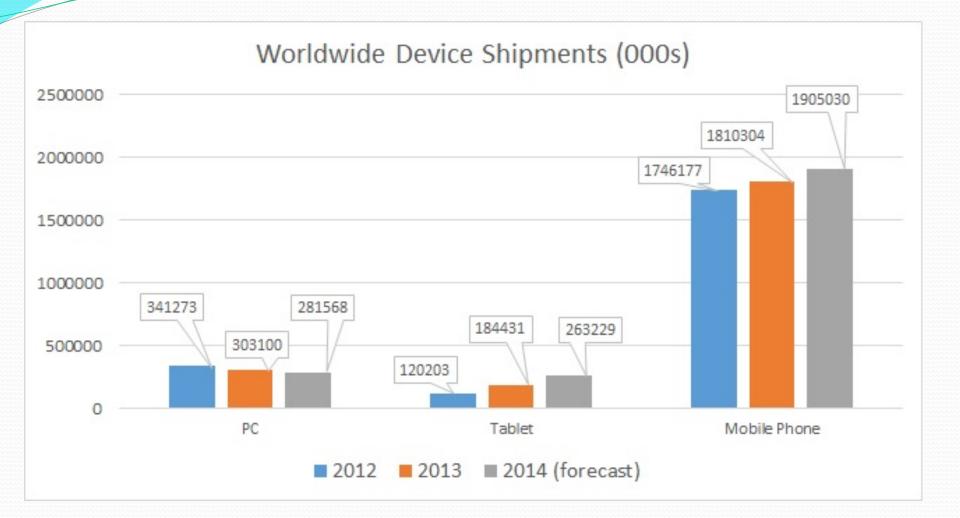

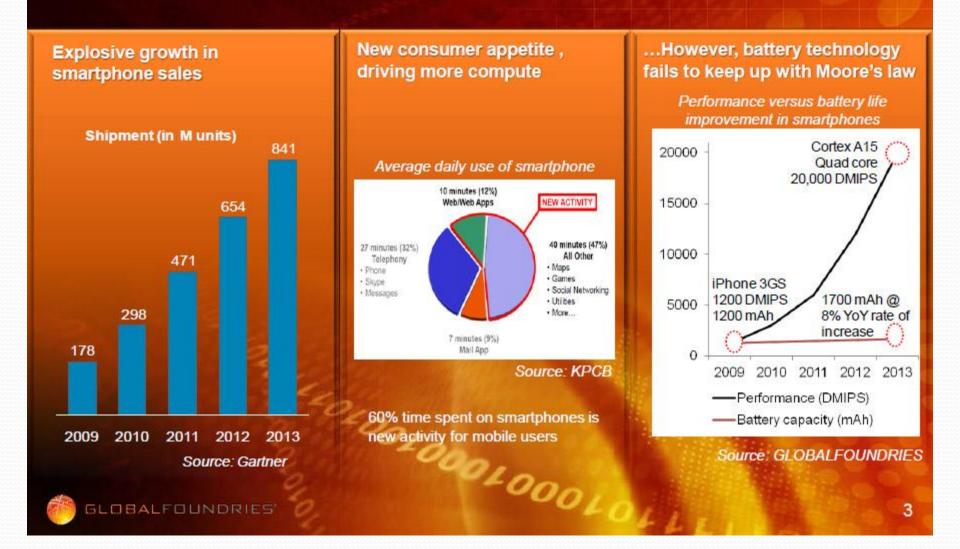

# The fast evolving market

### Mobile Internet Next Major Computing Cycle

Morgan Stanley

Source: Mary Meeker

\_\_\_\_\_

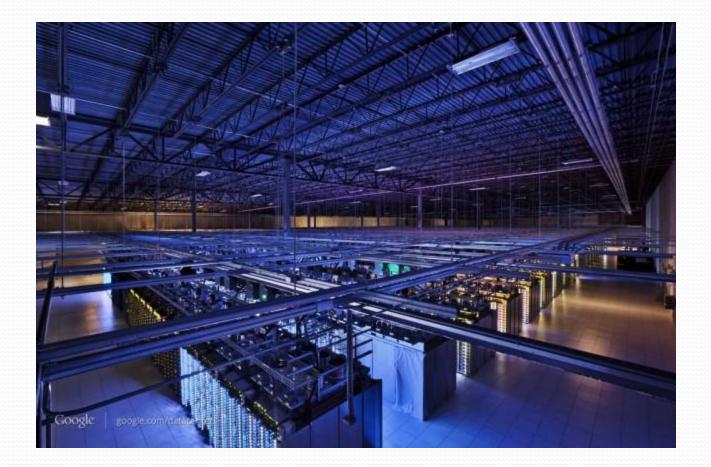

# Technology is driven by the market & industrial players

### Top 10 IC Wafer Capacity Leaders\* as of Dec-2013 (200mm-Equiv. Wafers per Month x1000)

| 2013<br>Rank | Company                | Headquarters<br>Region                | Installed<br>Capacity<br>(K w/m) | % of<br>Worldwide<br>Total |

|--------------|------------------------|---------------------------------------|----------------------------------|----------------------------|

| 1            | Samsung                | South Korea                           | 1,867                            | 12.6%                      |

| 2            | тѕмс                   | Taiwan                                | 1,475 10.0%                      |                            |

| 3            | Micron**               | Americas                              | 1,380 9.3%                       |                            |

| 4            | Toshiba/SanDisk        | Japan                                 | 1,177                            | 8.0%                       |

| 5            | SK Hynix               | South Korea                           | 1,035                            | 7.0%                       |

| 6            | Intel                  | Americas                              | 961                              | 6.5%                       |

| 7            | ST                     | Europe                                | 551                              | 3.7%                       |

| 8            | имс                    | Taiwan                                | 520                              | 3.5%                       |

| 9            | GlobalFoundries        | Americas                              | 482                              | 3.3%                       |

| 10           | ті                     | Americas                              | 441                              | 3.0%                       |

| _            | Total                  | _                                     | 9,889                            | 66.8%                      |

| ource: C     | Companies, IC Insights | *Includes shares<br>**Includes the fo |                                  | •                          |

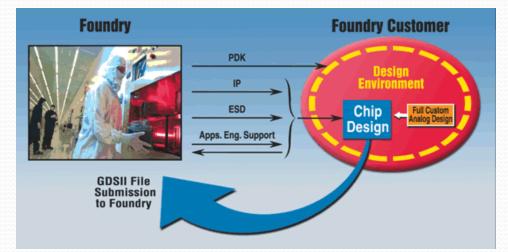

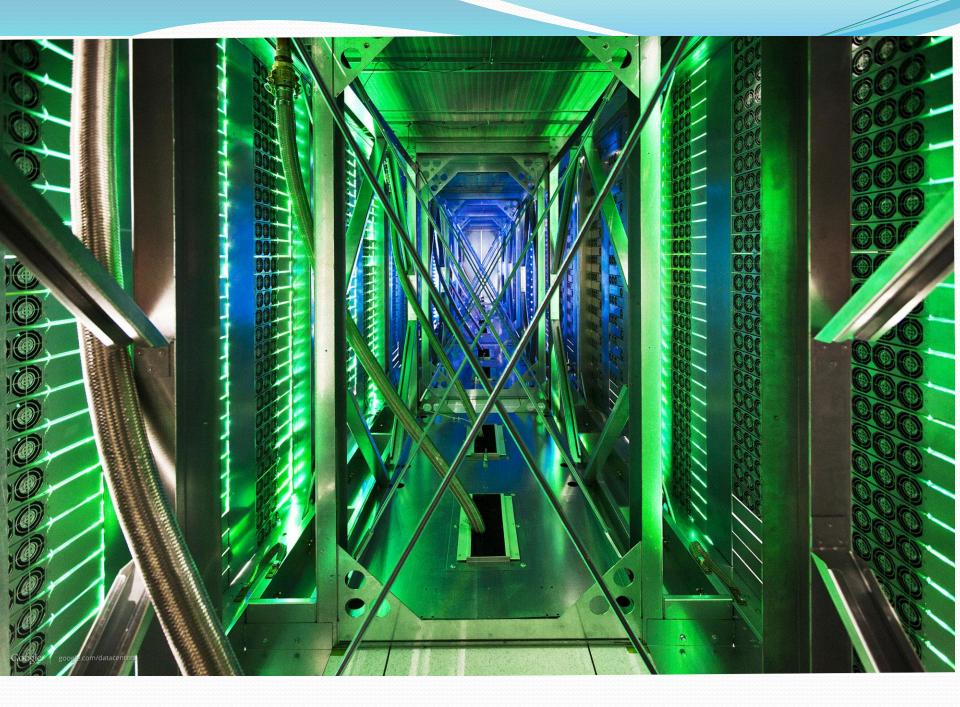

# Foundry and Chip Design

#### Wafer Fabs and Foundries

Standard processes

Increased througput

Improved utilization

**Better vields**

New revenues

Process Design Kit Intellectual Property

Chip Design

**PIC Designers and Users**

- First time right

- Fewer iterations

- Reduced chip cost

- Serve more applications

- Fab independent

#### http://www.techbriefs.com/compo nent/content/article/15547

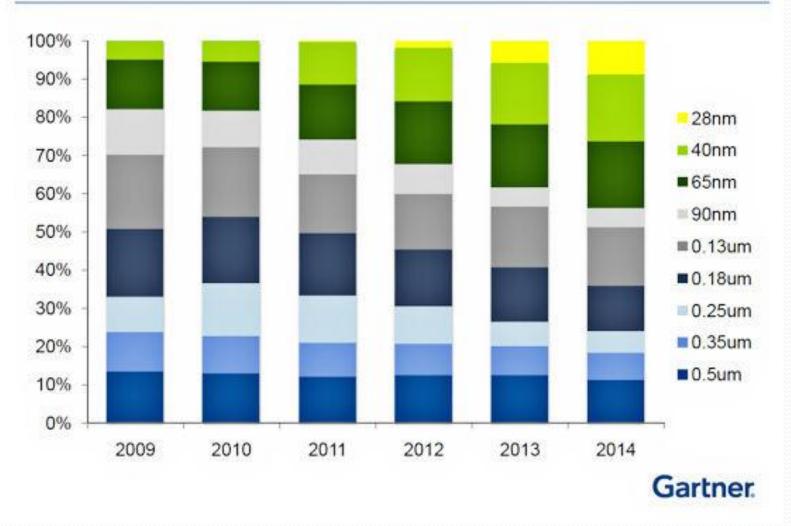

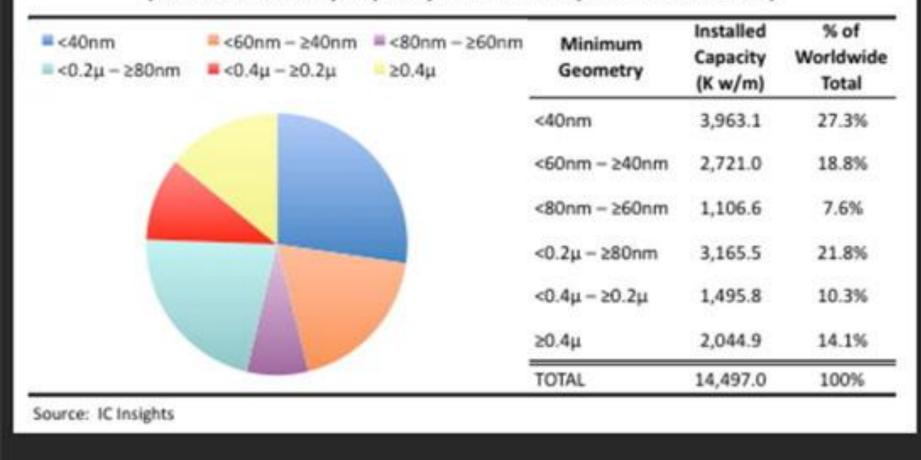

# Foundry Capacity by Technologies

#### Worldwide Capacity by Minimum Geometry as of Dec-2012 (Installed Monthly Capacity in 200mm-Equiv. Wafers x1000)

#### Figure 1

### Worldwide Capacity by Geographic Region as of Jul-2011 (Installed Monthly Capacity in 200mm-Equiv. Wafers x1000)

| Americas Europe | ■ Japan Korea                             | Region   | Installed<br>Capacity<br>(K w/m) | % of<br>Worldwide<br>Total |

|-----------------|-------------------------------------------|----------|----------------------------------|----------------------------|

|                 |                                           | Americas | 1,995.1                          | 14.7%                      |

|                 |                                           | Europe   | 1,109.3                          | 8.1%                       |

|                 |                                           | Japan    | 2,683.6                          | 19.7%                      |

|                 |                                           | Korea    | 2,293.5                          | 16.8%                      |

|                 | And a | Taiwan   | 2,858.3                          | 21.0%                      |

|                 | and a second second                       | China    | 1,208.9                          | 8.9%                       |

|                 |                                           | ROW      | 1,469.2                          | 10.8%                      |

|                 |                                           | TOTAL    | 13,617.8                         | 100%                       |

Source: IC Insights

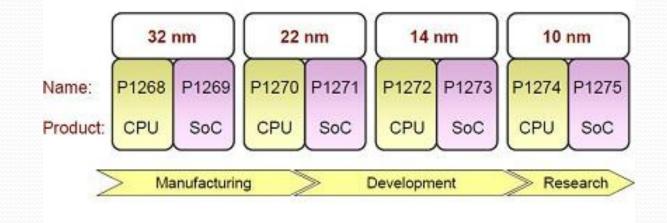

Perspectives from industrial players

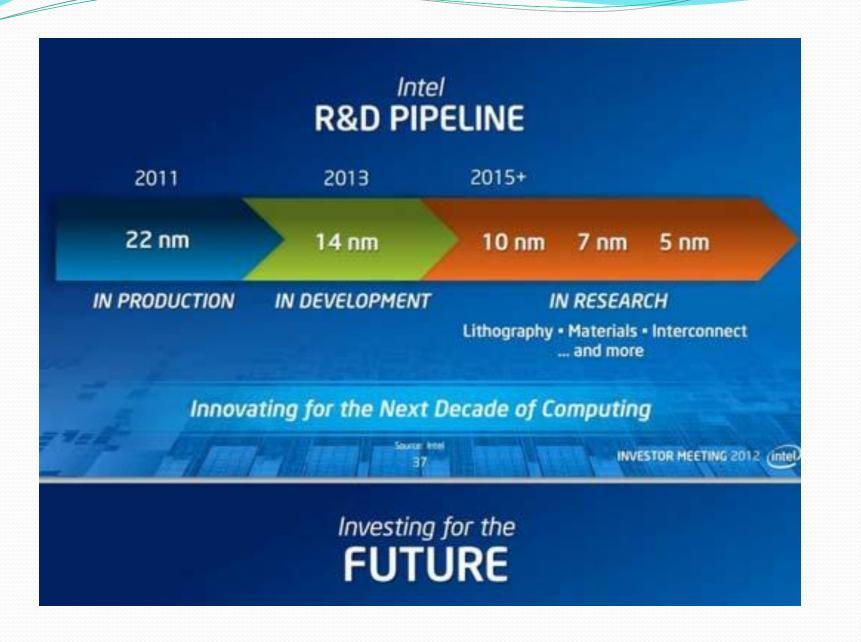

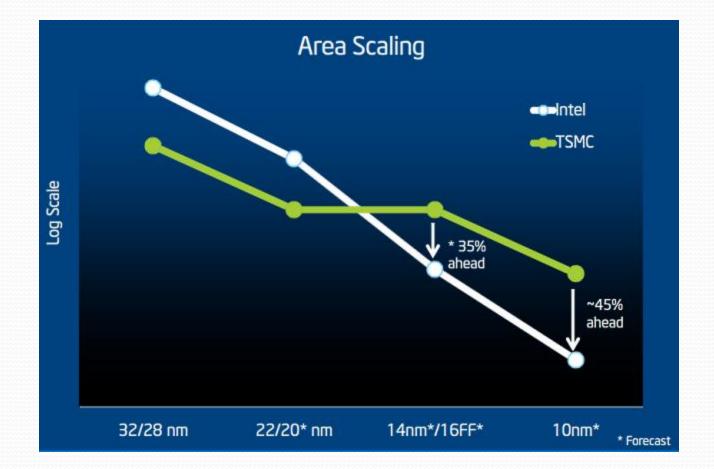

#### Intel Logic Technology Roadmap

Intel develops both CPU and SoC versions of each generation

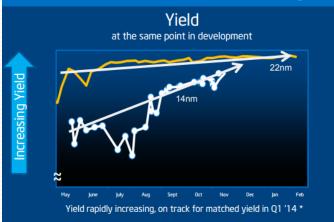

### Brief Update on14nm Status

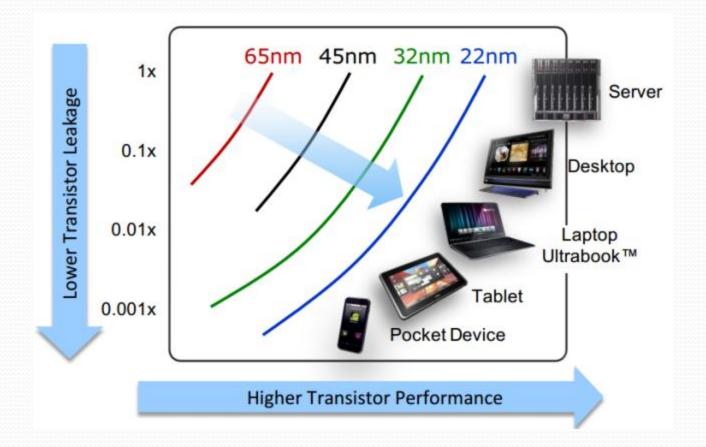

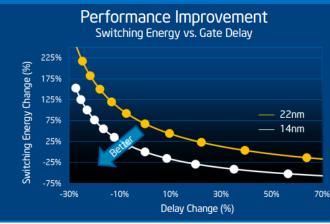

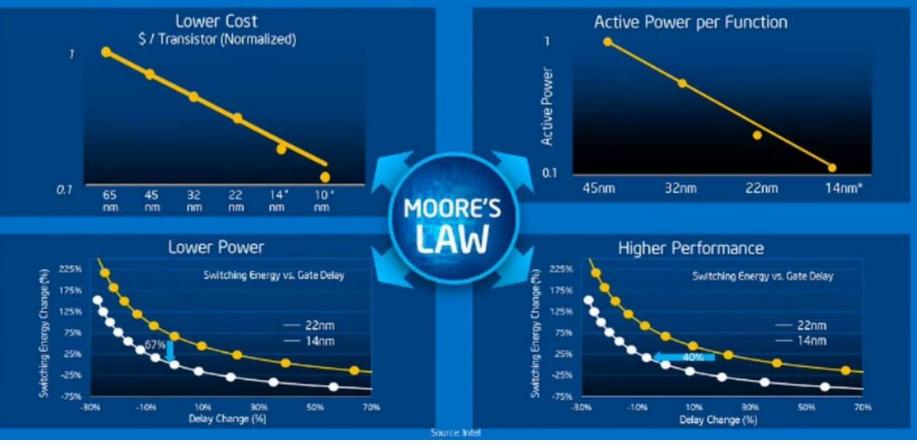

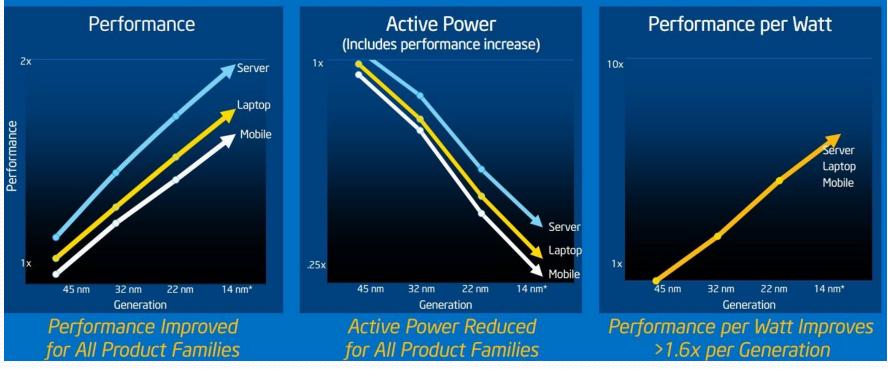

# Getting Benefits of Moore's Law Across all Value Vectors

### **Different Improvement Focus for Different Segments**

#### **Three Key Technology Enablers**

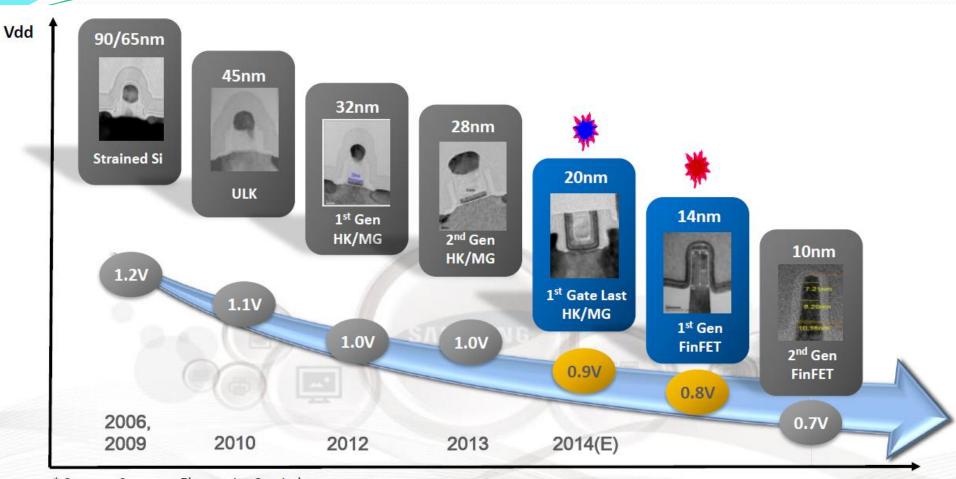

### Low Power Is Critical For Mobility Market

# Product Leadership Is More Than "Just The Fin"

\* Source : Samsung Electronics Co., Ltd.

**Process Node**

\*Vdd : Supplying voltage of drain

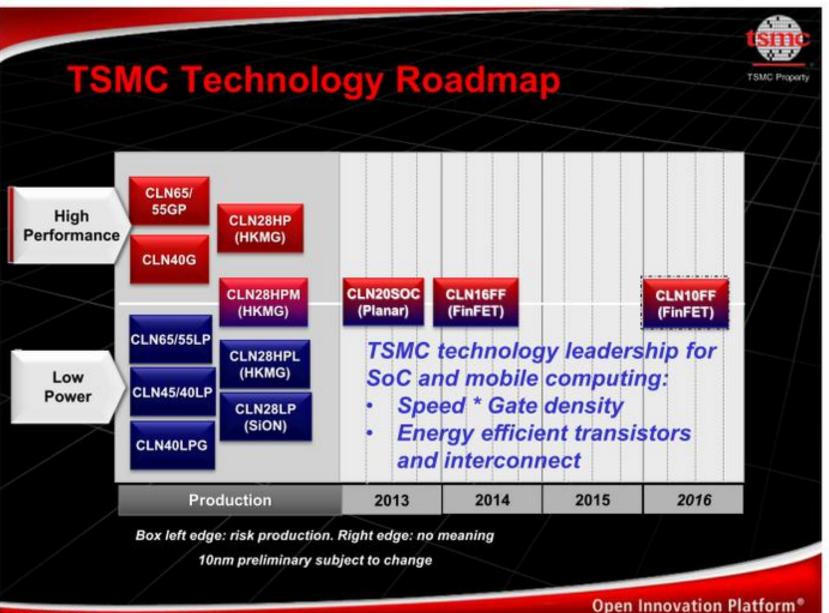

O 2011 TSMC, Ltd

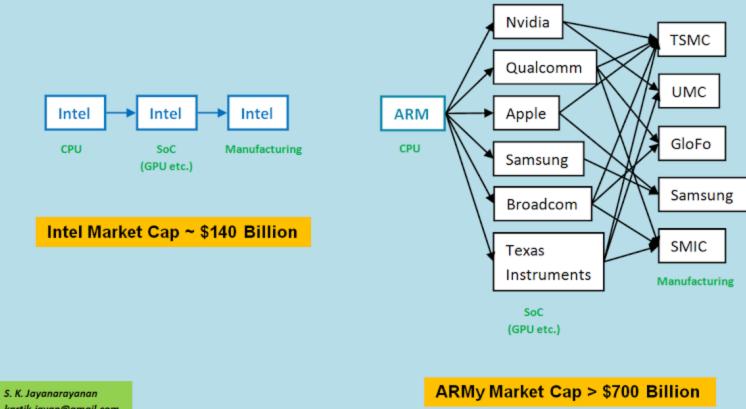

# The battle of chip architecture

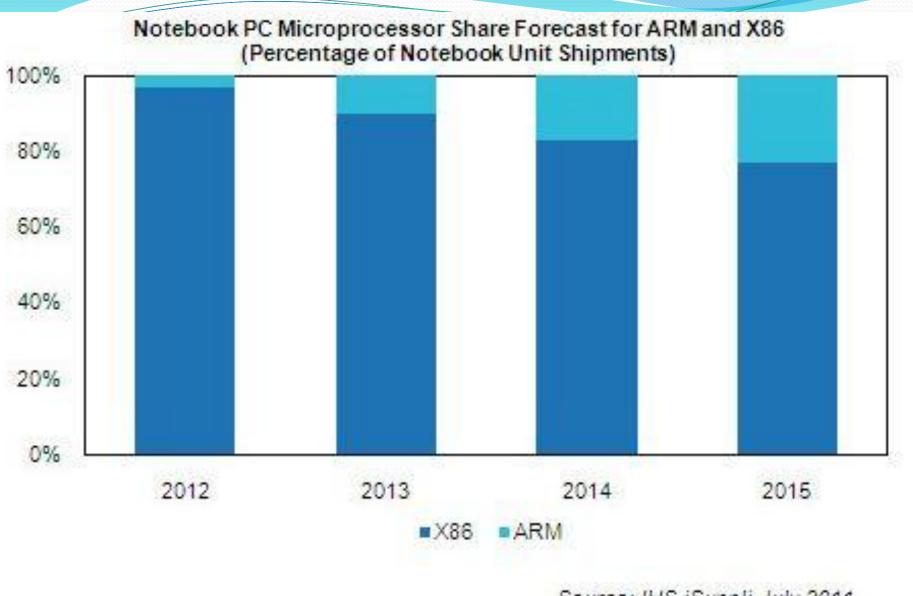

## Intel vs. ARM

ARMy Market Cap > \$700 Billion

S. K. Jayanarayanan kartik.jayan@gmail.com March 2012

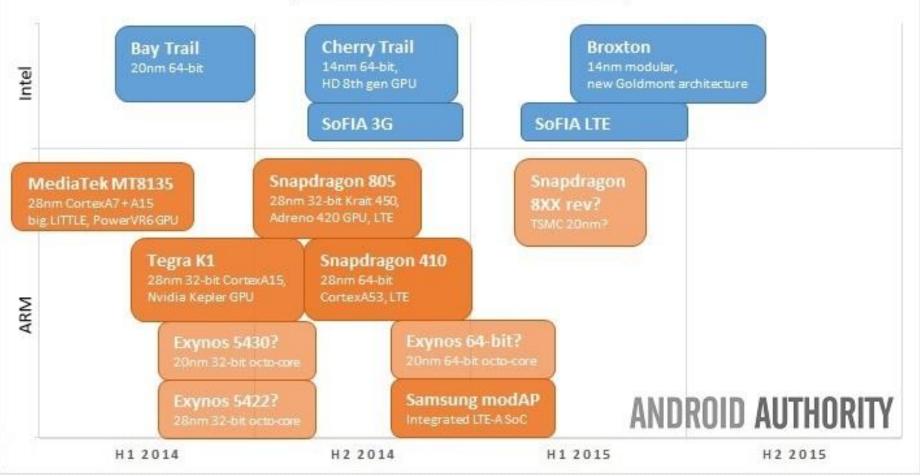

#### INTEL VS ARM ROADMAP

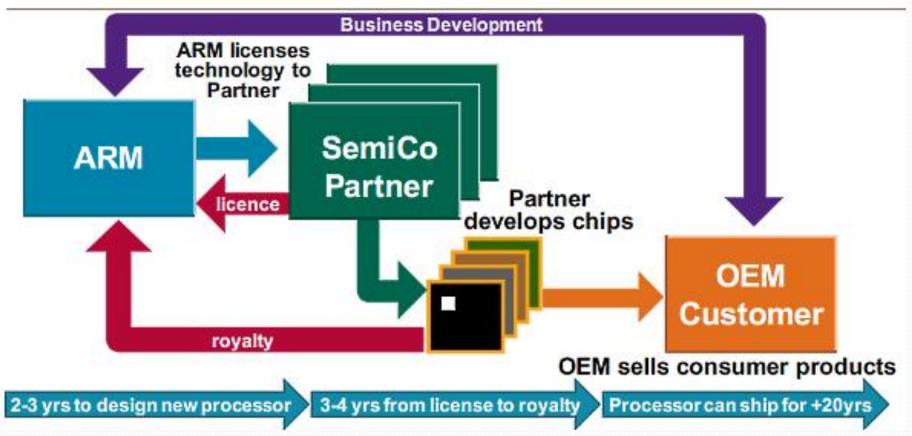

# **ARM Business Model**

Source: IHS iSuppli July 2011

### Silvermont Highlights

#### Better Performance

- Out of Order Execution engine

- New multi-core and system fabric architecture

- New IA instructions extensions (Core<sup>®</sup> Westmere level)

- New security and virtualization technologies

Better Power Efficiency

- Wider dynamic operating range

- Enhanced active and idle power management

#### Full Advantage of Intel<sup>®</sup> 22nm SoC Process Technology

- 3-D Tri-gate transistors tuned for SoC products

- Architecture and design cooptimized with the process

~3X the Performance Or ~5X Lower Power<sup>1</sup>

ted on the geometric mean of a variety of power and performance measurements access various benchmarks, benchmarks including Cardinaria including Cardinaria

Jean-Baptiste Contributor

FOLLOW

I cover technology innovation and investing from Silicon Valley. full bio 🏼

10/29/2013 @ 9:46PM 42,712 views TECH

# Exclusive: Intel Opens Fabs To **ARM** Chips

00 🎒 🕎 🕑 11 comments, 7 called-out

+ Comment Now

+ Follow Comments

As the old adage goes, if you can't beat them, join them. Well, that's exactly what Intel INTC-0.41% finally decided to do relative to its lagging mobile business.

At the ARM developers conference today, Intel partner Altera ALTR +0.32% announced that the world's largest semiconductor company will fabricate its ARM 64-bit chips starting next year. The announcement sent shockwaves through the technology industry as Intel is desperately trying to break ARM's supremacy in the mobile market. Unlike Intel, ARM Holdings of the U.K. doesn't manufacture chips but its designs are licensed 11 • 1 • • • • • •

### **Electronics** Weekly.com

| Home        | News                                                                                                        | Blogs | Multimedia | Companies | Events | Newsletters | Jobs |  |

|-------------|-------------------------------------------------------------------------------------------------------------|-------|------------|-----------|--------|-------------|------|--|

| You are her | You are here: Electronics Weekly > News > General > Intel to make multi-die 14nm finfet devices with Altera |       |            |           |        |             |      |  |

#### Intel to make multi-die 14nm finfet devices with Altera

🗊 no comment \mid 💄 richard wilson 🛛 🕜 28th March 2014 🛛 🖾 Get news by email

Altera and Intel are working together on the development of multi-die devices which integrate 14nm Stratix 10 FPGAs with memory, processors and analogue components in a single package.

The heterogeneous multi-die devices incorporate 3D silicon technology and Intel's 14nm Tri-Gate (finfet) process technology.

Intel is already manufacturing Altera's Stratix 10 FPGAs and system-on-chip devices (SoCs) using the 14nm Tri-Gate process.

Intel and Altera are currently developing test vehicles aimed at streamlining manufacturing and integration flows.

"Our partnership with Altera to manufacture next-generation FPGAs and SoCs using our 14nm Tri-Gate process is going exceptionally well," said Sunit Rikhi, vice president and general manager, Intel Custom Foundry.

"Our close collaboration enables us to work together in many areas related to semiconductor manufacturing and packaging," said Rikhi.

Together, both companies are building off one another's expertise with the primary focus on building industry-disrupting products."

According to Brad Howe, senior vice president of R&D at Altera, access to Intel's manufacturing and chip packaging capabilities is allowing the FPGA supplier to offer system-in-a-package products which are "critical to meeting overall performance requirements."

#### Related news:

Altera: 14nm Stratix and 20nm Arria FPGA details

#### **PROCESSORS** microprocessors

### Samsung teams with GlobalFoundries on 3D chips

Apr 17, 2014 3:15 PM 🛛 🖶

Samsung is partnering with chip manufacturer GlobalFoundries to increase the supply of low-power, high-speed chips for smartphones and tablets.

GlobalFoundries has licensed Samsung's 14-nanometer FINFET chip making process, which is used to manufacture 3D transistors. Those transistors will allow GlobalFoundries to make chips that are 20 percent faster and use 35 percent less power than chips made using its current 20-nanometer technology, the companies said.

GlobalFoundries doesn't use the chips itself. It's a foundry supplier, which means it makes chips for other companies that outsource their chip production, such as Advanced Micro Devices, Nvidia and Qualcomm.

Chip makers are constantly racing to build faster, more power-efficient chips, and the deal with Samsung will help GlobalFoundries compete better with other foundry suppliers such as Taiwan's TSMC.

In fact, GlobalFoundries had been pursuing its own 14-nanometer technology, which it planned to introduce this year. It has now dropped that technology, apparently deciding that Samsung's FINFET process is a better option.

# The big customers

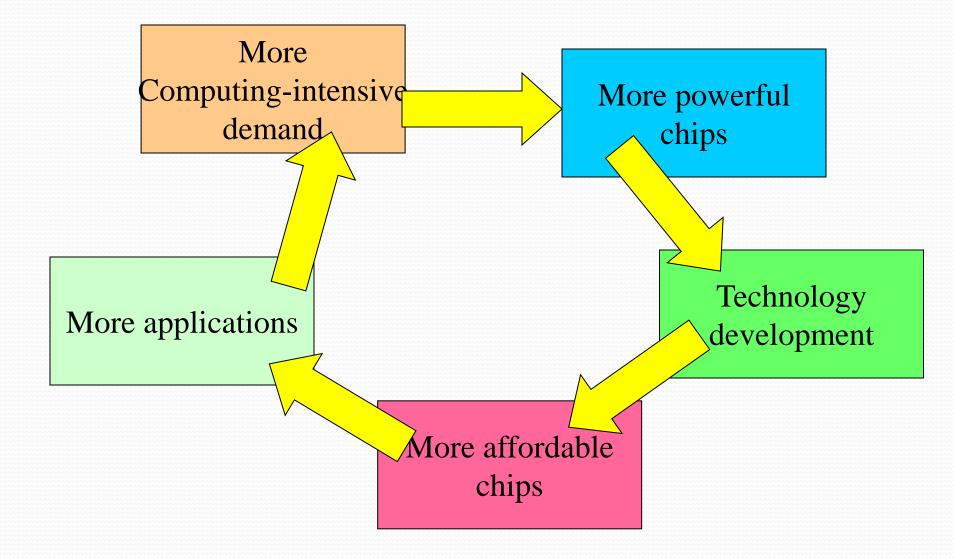

## The growth cycle